Classic battles: PC vs Mac, Emacs vs Vi, Tastes Great vs Less Filling, and certainly one that we debate around the Hackaday watercooler: command line or IDE? There’s something to be said for using good old command line tools, and even if you like to configure your favorite editor to be nearly an IDE, at least it is one you are familiar with and presumably leverage over several different uses.

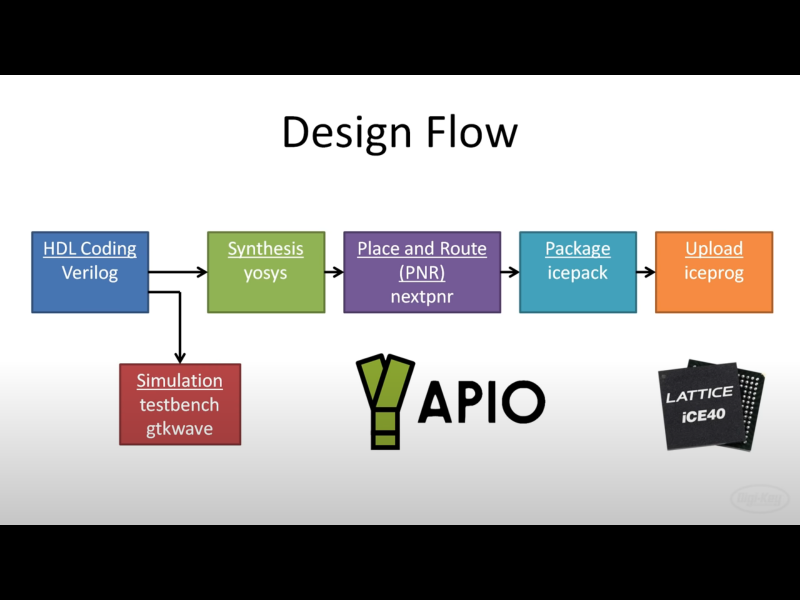

Most commercial FPGA tools come with a heavy-weight IDE. The open source tools for Lattice (IceStorm) typically is driven by the command line or a makefile. Until now. [Rochus-Keller] released …read more

Continue reading Open Source IDE for FPGAs as QtCreator Learns Verilog→